同步时序逻辑电路设计虚拟仿真实验

(1)实验目的

掌握同步时序逻辑电路实验的设计方法。

(2)实验环境

互动型数字逻辑虚拟实验平台IVDLEP

(3)实验内容

设计1001序列检测器。

(4)实验步骤

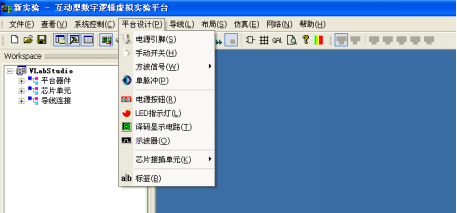

①打开“互动型数字逻辑虚拟实验平台”,选择“平台设计”菜单项,放置相应的平台器件,如图1所示。

图1 选择“平台设计”菜单

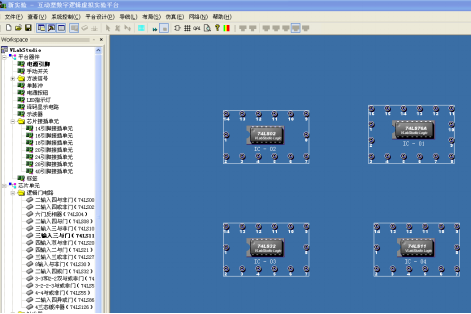

②根据逻辑功能,选择逻辑门,布置规划放置相应的“芯片接插单元”,如图2所示。

图2 装载“芯片接插单元”(换图)

③根据逻辑功能,在相应的“芯片接插单元”装配所选芯片,如图2-3所示。

图3 装配芯片

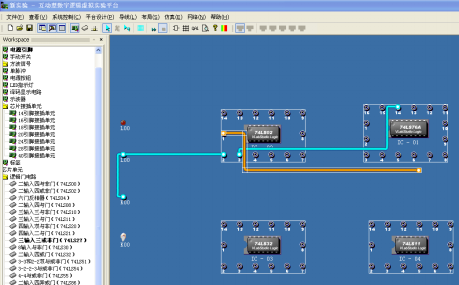

④根据逻辑功能,完成布线操作,如图4所示。

图4 布线

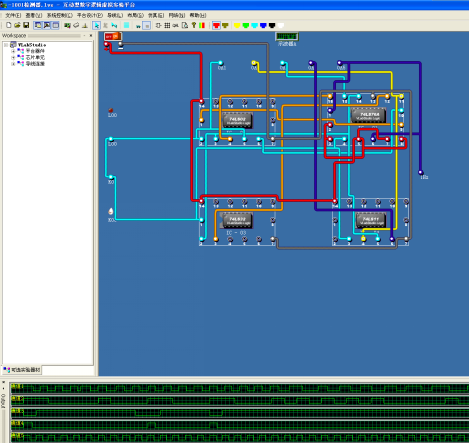

⑤保存文件,进行虚拟仿真,得出仿真结果,如图5所示。

图5 1001序列检测器虚拟仿真效果图

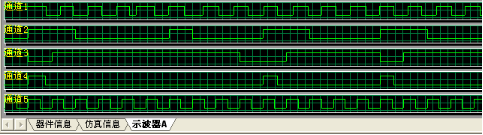

⑤随机输入序列,观察示波器波形观察输出Z的波形,1001序列检测器仿真结果,如图6所示。

图6 1001序列检测器仿真结果