二分频电路虚拟仿真实验

(1)实验目的

①掌握CPLD/FPGA设计方法之一——原理图输入的设计方法。

②熟悉二分频单元电路的实现方法

(2)实验环境

QuartusII平台

(3)实验内容

利用Altera公司的Cyclnoe系列中EP1C6Q240C8器件,采用原理图设计方式实现一个二分频单元电路。

(4)实验步骤

①工程建立

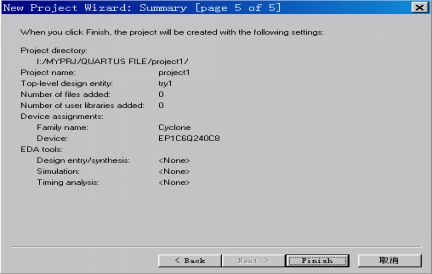

选择File菜单下New Project Wizard,按照提示完成输入工作目录和项目名称,加入已有的设计文件到项目,选择设计器件,选择第三方EDA综合、仿真和时序分析工具,建立项目完成,显示项目概要,完成后出现如图1所示的界面。

图1 项目概要

②原理图的输入

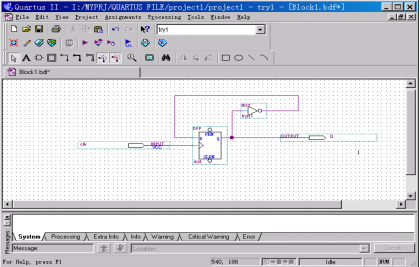

选 择File 菜单下新建图表/原理图文件,在设计方式选在Block Diagram/Schematic File,然后逐一添加D触发器、输入端口、输出端口和非门电路符号,按照二分频电路结构连接系统电路,将输入输出端口改名,如图2所示。单击保存按钮, 以try1 文件名保存,文件后缀为bdf。

图2 二分频设计输入图

③系统编译

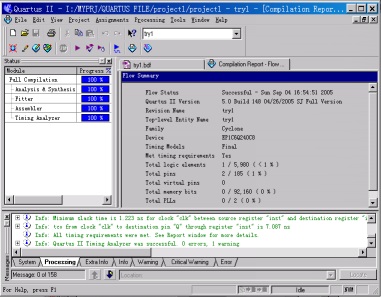

单击编译器快捷方式按钮,完成编译后,弹出菜单报告错误和警告数目,并生成编译报告如图3所示。

图3 完成编译的屏幕

④器件及管脚设定

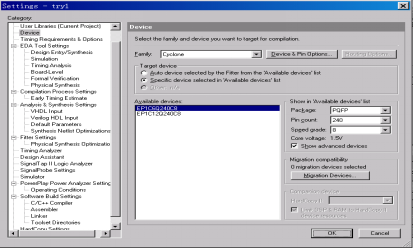

若需指定器件,选择Assignments菜单下Device选项,依据提示依次设置器件类型、器件型号,如图4所示。

图4 器件设置

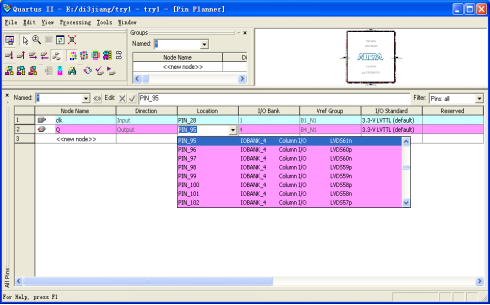

根据硬件接口设计,对芯片管脚进行绑定。选择Assignments菜单下Pins选项;双击对应管脚后Location空白框,出现下拉菜单中选择要绑定的管脚,如图5所示。

图5 管脚指定

⑤系统波形仿真

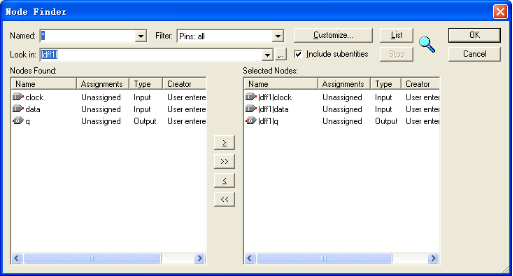

新 建波形仿真文件,保存为try2.vwf;在建立的波形文件左侧一栏中,点击鼠标右键,在弹出菜单中选择 Insert Node or Bus;选择Node Finder,将打开Node Finder 对话框,本试验对输入输出的管脚信号进行仿真,所以在Filter 中选择 Pins:all,点击List 按钮,如图6所示。

图6 Node Finder 对话框

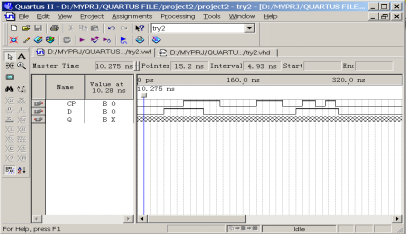

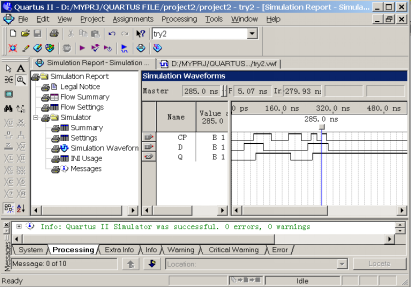

在 图6左栏中选择需要进行仿真的端口通过中间的按钮加入到右栏中,点击OK,端口加入到波形文件中;选择一段波形,通过左边的设置工具条,给出需要的值,设 置完成激励波形,保存后如图7所示;点击开始仿真快捷按钮,开始仿真,完成后得到波形如图8所示,根据分析,功能符合设计要求。

图7 设置好激励波形的波形文件

图8 波形仿真结果